# Charge Replacement in Hybrid Electrical Energy Storage Systems\*

Qing Xie, Yanzhi Wang, and Massoud Pedram

Electrical Engineering Department

University of Southern California

Los Angeles, CA, USA 90089

{xqing, yanzhiwa, pedram}@usc.edu

Younghyun Kim, Donghwa Shin, and Naehyuck Chang<sup>†</sup>

Dept. of EECS/CSE

Seoul National University

Seoul, Korea 151-744

{yhkim, dhshin, naehyuck}@elpl.snu.ac.kr

Abstract — Hybrid electrical energy storage (HEES) systems are composed of multiple banks of heterogeneous electrical energy storage (EES) elements with distinctive properties. Charge replacement in a HEES system (i.e., dynamic assignment of load demands to EES banks) is one of the key operations in the system. This paper formally describes the global charge replacement (GCR) optimization problem and provides an algorithm to find the near-optimal GCR control policy. The optimization problem is formulated as a mixed-integer nonlinear programming problem, where the objective function is the charge replacement efficiency. The constraints account for the energy conservation law, efficiency of the charger/converter, the rate capacity effect, and self-discharge rates plus internal resistances of the EES element arrays. The near-optimal solution to this problem is obtained while considering the state of charges (SoCs) of the EES element arrays, characteristics of the load devices, and estimates of energy contributions by the EES element arrays. Experimental results demonstrate significant improvements in the charge replacement efficiency in an example HEES system comprised of banks of battery and supercapacitor elements with a high-power pulsed military radio transceiver as the load device.

# I. INTRODUCTION

Electricity energy generation and consumption rates are typically not matched with each other. Conventional fossil fuel and nuclear power plants cannot immediately track the fluctuation of load demand. Furthermore, the output power levels of most renewable power sources strongly depend on various environmental factors (e.g., the solar irradiance or weather conditions), and therefore, not controllable. An electricity generation facility must be capable of accommodating the peak load demand at all times in order to avoid power outage. This requirement is typically met by over-provisioning the power generation facility at a significant capital investment cost. An alternative, and less expensive, solution is to store the excess energy produced at certain times of the day in electrical energy storage (EES) systems and to use the stored energy during the peak load times as needed. This solution (known as peak shaving) minimizes energy waste and provides stability to the power generation and distribution network. In summary, EES systems increase availability of the electrical energy, mitigate the supply-demand mismatches, and reduce the power generation capacity required to meet the peak-power demand.

There are actual deployment practices of grid-scale EES systems which mitigate the gap between the supply and demand [1, 2]. Most current EES systems are homogeneous, that is, they consist of a single type of EES element, and therefore,

suffer from a fundamental shortcoming that plagues every homogeneous EES system: key figures of merit (normalized with respect to capacity) of any homogeneous EES system cannot be any better than those of its individual EES elements.

No available EES element can fulfill all the required performance metrics of an ideal storage means (e.g., high power/energy density, low cost/weight per unit capacity, high round-trip efficiency, and long cycle life.) This shortcoming of the EES elements along with the homogenous nature of the current EES systems have prevented the adoption of a wide range of socially and economically beneficial technologies, such as grid-scale EES systems and electric vehicles. Hence, overcoming the limitation of homogeneous EES systems is an important undertaking, one that has motivated our research.

Hybrid EES (HEES) systems [3, 4] are EES systems that comprise of two or more heterogeneous EES elements, where each type has its unique strengths and weaknesses. Yet, the HEES system can be designed in such a way that it offers the characteristics of an ideal storage means in much the same way that a hybrid memory system in today's computer systems provides low access delay, high density, and low cost all at the same time. Based on the properties of the HEES system and characteristics of load devices (or power sources), the corresponding charge management policies aiming to achieve nearoptimal performance of the HEES must be developed. The appropriate charge management policies, including charge migration, charge allocation, charge replacement and HEES bank re-configuration, can exploit the strength of each type of EES element while hiding the shortcomings. Therefore, it achieves a combination of performance metrics that is superior to that of any of its individual EES components.

This paper focuses on developing the near-optimal charge replacement<sup>1</sup> control policy which determines the most suitable discharging current profile. More precisely, it determines the discharging current of each EES bank, from zero to a maximum limit, for a give load demand. The optimal charge replacement policy maximizes the charge replacement efficiency while satisfying the load demands.

Some previous work introduced hybrid discharge [5, 6] and composite EES system [7]. However, they either have limitations in setting the discharging current as desired [5, 6] or mainly focus on feasibility of energy management scheme [7]. To our knowledge, this is the first paper that provides an algorithm to determine the near-optimal simultaneous discharging of multiple heterogeneous EES banks for a given load profile. In this paper, we introduce a generalized HEES architecture and build the corresponding electrical circuit models for power converters and EES element arrays. We formulate the global charge replacement (GCR) optimization problem and propose

<sup>\*</sup>This research is sponsored in part by a grant from the National Science Foundation, and by the Brain Korea 21 Project, IC Design Education Center (IDEC), and Mid-career Researcher Program through NRF grant funded by the MEST (No. 2010-0017680). The ICT at Seoul National University provides research facilities for this study.

<sup>†</sup>Corresponding Author

<sup>&</sup>lt;sup>1</sup>Charge replacement implies discharge from the EES elements. This term is borrowed from computer memory management.

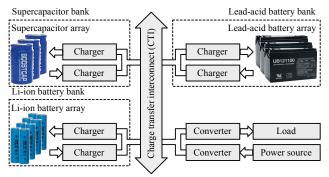

Fig. 1. HEES system architecture.

an efficient algorithm to find the near-optimal GCR control policy based on the state of charges (SoCs) of EES element arrays and characteristics of load devices. We also take into account the efficiency of power converters, the rate capacity effect, the self-discharge, effect of internal resistance of the EES element arrays, and fluctuation of the load demands. We examine our GCR control policy in a couple of representative cases with different operation time and different number of EES banks. Experimental results show improvements up to 30% compared to a good baseline in terms of the GCR efficiency.

#### II. HEES SYSTEMS

#### A. Related Work

Batteries generally have high energy capacity but limited power capacity, while supercapacitors are the opposite. Complementary (hybrid) discharging a battery and a supercapacitor provides both high energy and power capacity. As the simplest hybrid discharging, a parallel connection of a supercapacitor with a Li-ion battery enables a higher discharging current and reduces the impact of the rate capacity effect thanks to the supercapacitor [5, 6]. However, the parallel connection is limited to passive discharging current controllability. The proportion among multiple discharging currents is determined by intersection of their V-I characteristics. A constant current charger can isolate the battery from supercapacitor and in turn provide higher order degree of freedom in maintaining a desired charging current regardless of the SoC of the supercapacitor [8]. However, this method does not allow simultaneous discharging of both the battery and the supercapacitor.

## B. HEES System Architecture

A conceptual simplified block diagram of HEES system architecture is illustrated in Figure 1. The system is comprised of multiple heterogeneous EES banks connecting to each other through Charge Transfer Interconnect (CTI). Each EES bank contains an EES (element) array and two chargers, which enable charge transfer incoming to and outgoing from the EES arrays through CTI regardless of their different SoCs and power rating values. The power source and load devices are connected to the HEES system through DC-DC converters to maintain the voltage-level compatibility [3]. In each bank, the EES array is composed of multiple homogeneous EES elements with the same SoC since a typical single EES element has low voltage rating and small energy capacity. Generally, supercapacitor banks can be used as temporary energy storage for high intermittent power, while battery banks are used for long-term large-scale energy storage. Besides charge replacement, other charge management policies such as bank re-configuration, charge migration and charge allocation should also be developed with the consideration of EES element properties and source/load characteristics.

## C. Charge Replacement

Charge replacement selects EES banks to be discharged and determines the discharging current of each selected EES bank

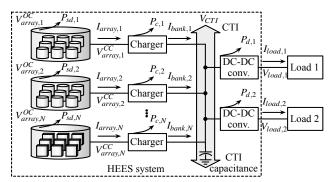

Fig. 2. Charge replacement system schematic.

to support a given load demand. Effective charge replacement algorithms need to take into account the distinct properties of EES element arrays, efficiencies of the power converters, and characteristics of the load devices. The best-suited EES banks and corresponding discharging currents may vary over time according to the load demands and SoC changes of storage array. The proposed near-optimal charge replacement algorithm can effectively determine the discharging current of each EES bank to satisfy load demands as well as maximize the GCR efficiency during the whole discharge process.

Figure 2 shows the conceptual schematic of the charge replacement problem. The HEES system is comprised of Nheterogeneous EES banks, denoted by a set  $S = \{1, 2, ..., N\}$ , where each bank consists of an EES element array, a discharging control charger and a charging control charger that connect the EES array to CTI. All the charging control chargers are turned off in the charge replacement problem and thus are removed from schematics for simplicity. The CTI has capacitances due to the input and output bulk capacitors of the chargers and converters. At time t, a subset of all EES banks  $S_{on}(t) \in S$  is turned on and provides power to CTI. We use  $V_{array, k}^{OC}(t)$  and  $V_{array, k}^{CC}(t)$  to denote open circuit terminal voltage (OCV) and closed circuit terminal voltage (CCV) of EES element array in the  $k^{th}$  bank, respectively. These two voltages are generally not equal to each other due to the internal resistances of the EES array. The relation between  $V_{array, k}^{OC}(t)$ and  $V_{array, k}^{CC}(t)$  is given in Section 3.1.1. Each EES array k has self-discharge with power rate of  $P_{sd, k}(t)$ . The input and output currents of the  $k^{th}$  discharging control charger are denoted by the array discharging current,  $I_{array, k}(t)$ , and the bank discharging current,  $I_{bank, k}(t)$ , respectively. The power loss of the  $k^{th}$  charger is denoted by  $P_{c,k}(t)$  and is a function of its input and output voltages and currents, as shown in Section 3.1.2. Each load device j is connected to the CTI through a DC-DC converter with conversion power loss  $P_{d,j}(t)$ . The operating voltage, current and power of the  $j^{th}$  load device are denoted by  $V_{load, j}(t)$ ,  $I_{load, j}(\bar{t})$  and  $P_{load, j}(t)$ , respectively.

## D. Voltage Feedback

Ideally, the CTI voltage is determined by the power balance between the loads and the banks. The incoming currents from the banks to CTI and the outgoing currents from CTI to the load devices are perfectly balanced. Thus we can control the bank discharging currents through discharge control chargers to achieve both the load power match as well as the CTI voltage control. However, in practice, the incoming and outgoing currents of the CTI may have discrepancy, especially during the transient period whenever the load current changes. In such a case, the currents mismatch is accumulated in the CTI capacitance (mostly the input capacitors of the DC-DC converter and the output capacitors of the chargers) and increases or de-

creases the CTI voltage.

The chargers themselves have a feedback control loop so that the desired output current could be maintained at all times without additional external control. In addition to that, we deploy an outer feedback monitoring the CTI voltage at all times based on real-time software on top of the charger output current control. We adjust the charger output current values to maintain the CTI voltage by tracking the target value. Such a cascaded feedback control can stably maintain the discharging currents and CTI voltage as desired.

## III. PROBLEM FORMULATION

#### A. Bank Model

# A.1 EES Element Array

Without loss of generality, this paper introduces a global charge replacement problem with two representative EES elements to deliver the main concepts: Li-ion battery and supercapacitor. We use an electronic circuit model in [9] for the Li-ion battery model, which is suitable for developing a mathematical formulation. The relation between the OCV and the CCV of a battery array, denoted by  $V^{OC}$  and  $V^{CC}$ , is given by:

$$V_{array}^{OC}(t) = V_{array}^{CC}(t) + V_{tl}(t) + V_{ts}(t) + I_{array}(t) \cdot R_s, \tag{1}$$

where  $V_{tl}(t)$  and  $V_{ts}(t)$  are the voltage drops across the internal capacitances,  $I_{array}(t)$  is the array current and  $R_s$  is the internal series resistance. Similar relation can be applied to supercapacitor element arrays in which the internal capacitances are negligible.

A primary disadvantage of the supercapacitor is the high self-discharge rate. A supercapacitor may lose more than 20% of its stored energy per day even if no load is connected to it [3]. Such a high self-discharge rate plays an important role in GCR problem which may last for a couple of hours. The power loss at time t due to self-discharge is given by:

$$P_{sd}(t) = V_{array}^{OC}(t) \cdot I_{sd}(t) = C_{cap} \left( V_{array}^{OC}(t) \right)^2 / \tau, \tag{2}$$

where  $I_{sd}(t)$  is the self-discharge current,  $C_{cap}$  is the capacitance of the supercapacitor array and  $\tau$  is the self-discharge time constant. The self-discharge of battery is negligible.

The rate capacity effect of batteries specifies the fact that the available discharging time of a battery element array is strongly dependent on the array discharging current. According to the Peukert's Law [10], the empirical relation between the available discharging time and discharging current can be expressed as  $C_p = I^{\gamma}t$ , where  $C_p$  is the nominal capacity (in unit of  $A \cdot h$ , usually defined as the capacity at one-ampere discharge rate), I is the actual array discharging current, t is the discharging time and t is the Peukert constant (typically between 1.1 and 1.3.) In contrast, the rate capacity effect of supercapacitor arrays is negligible (t = 1.)

Therefore the power rate drawn from an EES element array due to discharge can be expressed as:

$$P_{drawn}(t) = \begin{cases} V_{array}^{OC}(t) \cdot I_{array}(t) + P_{sd}(t), & \text{supercap arrays} \\ V_{array}^{OC}(t) \cdot I_{array}^{\gamma}(t), & \text{battery arrays} \end{cases}$$

(3)

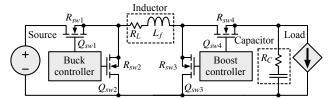

## A.2 Charger and DC-DC Converter

A charger is a switching converter which can regulate its output current to a desired value according to our proposed algorithm. In this paper, we use a PWM (pulse width modulation) buck-boost switching converter model as the charger model, as shown in Figure 3. The input voltage, input current, output voltage and output current of the charger are denoted by  $V_{in}$ ,  $I_{in}$ ,  $V_{out}$  and  $I_{out}$ , respectively. Depending on the relation between  $V_{in}$  and  $V_{out}$ , the charger has two operating modes:

Fig. 3. Buck-boost converter circuit model.

the buck mode (if  $V_{in} > V_{out}$ ) and otherwise the boost mode. When the charger is turned on, the power loss  $P_c^{on}$  consists of three components: conduction loss  $P_{cdct}$ , switching loss  $P_{sw}$  and controller loss  $P_{ctrl}$  [11], among which  $P_{sw}$  and  $P_{ctrl}$  are independent of the output current  $I_{out}$ . When the charger is turned off, the power loss is zero because the controller is turned off. Therefore, the power loss  $P_c$  is given by:

$$P_c = P_c^{on} \cdot x_c = (P_{cdct} + P_{sw} + P_{ctrl}) \cdot x_c, \tag{4}$$

where  $x_c$  is a binary variable with the interpretation that  $x_c = 1$  if the charger is turned on and  $x_c = 0$  otherwise.

In the buck mode, the power loss components are given by:

$$\begin{split} P_{cdct} = & I_{out}^{2} \cdot (R_{L} + D \cdot R_{sw1} + (1 - D) \cdot R_{sw2} + R_{sw4}) \\ & + 1/12 \cdot (\Delta I)^{2} \cdot (R_{L} + D \cdot R_{sw1} + (1 - D) \cdot R_{sw2} + R_{sw4} + R_{C}), \\ P_{sw} = & V_{in} \cdot f_{s} \cdot (Q_{sw1} + Q_{sw2}), \\ P_{ctrl} = & V_{in} \cdot I_{controller}, \end{split}$$

(5)

where  $D = V_{out}/V_{in}$  is the PWM duty ratio and  $\Delta I = V_{out} \cdot (1 - D)/(L_f \cdot f_s)$  is the maximum current ripple;  $f_s$  is the switching frequency;  $I_{controller}$  is the operating current of the controller;  $R_L$  and  $R_C$  are the equivalent series resistances of the inductor L and capacitor C, respectively;  $R_{swi}$  and  $Q_{swi}$  are the turn-on resistance and gate charge of  $i^{th}$  MOSFET switch in Figure 3, respectively.

In the boost mode, the power loss components are given by:

$$\begin{split} &P_{cdct} = \\ &(\frac{I_{out}}{1-D})^2 \cdot (R_L + D \cdot R_{sw3} + (1-D) \cdot R_{sw4} + R_{sw1} + D \cdot (1-D) \cdot R_C) \\ &+ 1/12 \cdot (\Delta I)^2 \cdot (R_L + D \cdot R_{sw3} + (1-D) \cdot R_{sw4} + R_{sw1} + (1-D) \cdot R_C), \\ &P_{sw} = V_{out} \cdot f_s \cdot (Q_{sw3} + Q_{sw4}), \\ &P_{ctrl} = V_{in} \cdot I_{controller}, \end{split}$$

(6)

where  $D=1-V_{in}/V_{out}$  and  $\Delta I=V_{in}\cdot D/(L_f\cdot f_s)$  in this case. We use the same model for the DC-DC converters which regulate the load voltages. The power loss of the  $j^{th}$  DC-DC converter, denoted by  $P_{d,j}$ , is also given by (4)~(6) with different set of parameters, input/output voltages and currents.

## B. Optimization Problem Formulation

The charge replacement problem is constrained by energy conservations. Let's consider a discharge process from time 0 to T. As illustrated in Figure 2, the power received by CTI is used to drive all the load devices and DC-DC converters, i.e., at time  $t \in [0,T]$ , we have:

$$P_{CTI}(t) = V_{CTI}(t) \sum_{k=1}^{N} I_{bank, k}(t) = \sum_{i=1}^{M} (P_{load, j}(t) + P_{d, j}(t)), \quad (7)$$

where N and M stand for the total number of EES banks and load devices, respectively. The power transferred from the  $k^{th}$  EES array to the  $k^{th}$  charger consists of the power received by CTI and the power loss in the charger, i.e.,

$$P_{array, k}(t) = V_{array, k}^{CC}(t) \cdot I_{array, k}(t) = V_{CTI}(t) \cdot I_{bank, k}(t) + P_{c, k}(t)$$

$$= V_{CTI}(t) \cdot I_{bank, k}(t) + P_{c, k}^{on}(t) \cdot x_{c, k}(t), \forall k \in S,$$

(8)

where  $V_{in}$ ,  $I_{in}$ ,  $V_{out}$  and  $I_{out}$  of the  $k^{th}$  charger are  $V_{array, k}^{CC}(t)$ ,  $I_{array, k}(t)$ ,  $V_{CTI}(t)$  and  $I_{bank, k}(t)$ , respectively;  $x_{c, k}(t) = 1$  if  $k \in S_{on}(t)$ , i.e., the  $k^{th}$  charger is turned on, and  $x_{c, k}(t) = 0$  otherwise.

We assume that the initial EES element array OCVs  $V_{array,\ k}^{OC}(t)\big|_{t=0},\ \forall k\in S$  can be known based on the initial EES array SoCs, using the SoC-OCV relations [9]. We also assume that the load profile, i.e.,  $P_{load,\ j}(t)$  and  $V_{load,\ j}(t)$  for  $t\in[0,T]$ , is given or predictable. The global charge replacement (GCR) optimization problem can be formally described as follows:

**Given:**

$$V_{array, k}^{OC}(t)\big|_{t=0}$$

,  $\forall k \in S, V_{load, j}(t)$  and  $P_{load, j}(t)$  for  $1 \le j \le M$  and  $t \in [0, T]$ .

**Find:**  $V_{CTI}(t)$ ,  $S_{on}(t)$ , and  $I_{bank, k}(t)$ , for  $\forall k \in S$  and  $t \in [0, T]$ . **Maximize:** the GCR efficiency, defined as:

$$\eta_{GCR} = \int_0^T \sum_{j=1}^M P_{load, j}(t) dt / \int_0^T \sum_{k=1}^N P_{drawn, k}(t) dt, \quad (9)$$

in which  $P_{drawn, k}(t)$  can be calculated by (3).

# Subject to:

i) energy conservation: (7), (8) are satisfied.

ii) charge conservation: SoC(t) for  $k^{th}$  element array:

$$SoC_k(t) = SoC_k(0) - \int_0^t [P_{drawn, k}(\tau) / V_{array, k}^{OC}(\tau)] d\tau / C_k^{full}$$

(10)

where  $C_k^{full}$  is the full charge of  $k^{th}$  element array. iii) the OCV-SoC relation for battery [9] and supercapacitor (square-root function), and the OCV-CCV relation (1). iv) the bank discharging current is no less than zero, and the array discharging current is no more than a maximum value

$$I_{bank, k}(t) \ge 0, I_{array, k}(t) \le I_{array, k}^{max}, \forall t \in [0, T], \forall k \in S, \quad (11)$$

if  $I_{bank, k}(t) = 0$ , the charger is turned off, i.e.  $k \notin S_{on}(t)$ .

## IV. OPTIMIZATION METHOD

We solve the GCR optimization problem in three steps. First we propose a near-optimal algorithm for the instantaneous charge replacement (ICR) problem obtained by letting  $T \to 0$  in the GCR problem formulation. Then, we globally consider the whole discharge process and assign the energy demands to the supercapacitor banks and battery banks. Finally, we solve the GCR problem in a discrete time space by performing the near-optimal ICR algorithm at each decision epoch with additional constraints derived from results in Step 2.

# A. Instantaneous Charge Replacement

As the ICR problem implies that  $T \to 0$ , we omit the time index t in the GCR problem formulation for simplicity in writing. We have EES array OCVs  $V_{array, k}^{OC}$ ,  $\forall k \in S$  derived from the EES array SoC values, and the load profile  $P_{load, j}$  and  $V_{load, j}$  for  $1 \le j \le M$ . The control variables are  $S_{on}$  (or  $x_{c, k}$ ,  $\forall k \in S$ ),  $V_{CTI}$  and  $I_{bank, k}$ ,  $\forall k \in S$ . The objective function to be minimized is (derived from (9)):

$$P_{drawn}^{total} = \sum_{k=1}^{N} P_{drawn, k} = \sum_{k=1}^{N} V_{array, k}^{OC} \cdot I_{array, k}^{\gamma_k} + P_{sd, k},$$

(12)

We derive the constraints from (7), (8) and (11) by omitting time index t. The ICR optimization is a mixed-integer nonlinear programming problem due to the existence of binary control variables  $x_{c, k}, \forall k \in S$ , and therefore NP-complete.

We first consider a simplified version of ICR (SICR) optimization problem to find the optimal  $I_{bank, k}$ ,  $\forall k \in S_{on}$  values

aiming at minimization of  $P_{drawn}^{total}$ , under the assumption that the set  $S_{on}$  and values  $V_{CTI}$ ,  $V_{array,\,k}^{CC}$  are given. In the SICR problem, the charger power loss  $P_{c,\,k}$  is a quadratic function of  $I_{bank,\,k}$  according to (4)~(6), and  $x_{c,\,k}$  is always one. Therefore, the array discharging current  $I_{array,\,k}$  becomes a convex function of  $I_{bank,\,k}$  according to (8). In addition, according to (3),  $\gamma_k$  is greater than (for battery arrays) or equal to (for supercapacitor arrays) one. The objective function (12) becomes a convex function of  $I_{bank,\,k}$ ,  $\forall k \in S_{on}$  as well due to the rules of convexity of composite functions [12]. Moreover, the inequality constraint (11) is convex, and the equality constraint (7) is affine over the control variables of  $I_{bank,\,k}$ ,  $\forall k \in S_{on}$ . The constraint (8) is already integrated into the objective function. Finally, the SICR problem is a convex optimization problem and can be solved in polynomial time.

We propose the following three heuristics to determine  $S_{on}$ ,  $V_{CTI}$  and  $V_{array, k}^{CC}$ , which are assumed given in deriving SICR problem.

**Heuristic A**: Let us assume that the optimal objective function  $P_{drawn}^{total}$  is a quasi-convex function with respect to  $V_{CTI}$ . We propose to solve a SICR problem with a fixed  $V_{CTI}$  value, and efficiently search feasible region of  $V_{CTI}$  to get the optimal  $V_{CTI}$  value. Simulation results validate the assumption of quasi-convexity and prove the efficiency of searching for the best-suited  $V_{CTI}$  value.

**Heuristic B**: We start from the initial  $S_{on} = S$  and find the final  $S_{on}$  set in an iterative manner. In each iteration, we only consider the banks  $k \in S_{on}$  in SICR problem, and thus  $x_{c, k}$  is always one. We update  $S_{on}$  by excluding those banks whose discharging current  $I_{bank, k}$  is smaller than the threshold value at the end of iteration.

**Heuristic C**: We start from the initial  $V_{array, k}^{CC} = V_{array, k}^{OC}$  and find the final  $V_{array, k}^{CC}$  value in an iterative manner. In each iteration, we solve SICR problem with  $V_{array, k}^{CC}$  assumed to be fixed and update  $V_{array, k}^{CC}$  using (1) at the end of the iteration.

We finally obtain the near-optimal solution to the ICR problem by iteratively solving the SICR problem. The complete algorithm is given in Algorithm 1.

## Algorithm 1: Near-Optimal ICR Solver.

```

Input: V_{array, k}^{OC}, \forall k \in S, P_{load, j} and V_{load, j} for 1 \le j \le M, CTI voltage range [V_{CTI}^{min}, V_{CTI}^{max}], threshold values V_{\varepsilon} and I_{\varepsilon}

```

**Output**: Near-optimal bank discharging current set  $\{I_{bank,\ k}^{opt}, \forall k \in S\}$ , corresponding set  $S_{on}^{opt}$  and CTI voltage  $V_{CTI}^{opt}$

```

\begin{array}{ll} \textbf{1 repeat} \\ \textbf{2} & \text{Initialize } S_{on} \leftarrow S, V_{array, \ k}^{CC} \leftarrow V_{array, \ k}^{OC}, \forall k \in S_{on} \\ \textbf{3} & \textbf{repeat} \\ \textbf{4} & \text{Update near-optimal bank discharging current set:} \\ & \{I_{bank, \ k}, \forall k \in S_{on}\} \leftarrow \text{solve SICR}(V_{CTI}, S_{on}, \\ & \{V_{array, \ k}^{CC}, \forall k \in S_{on}\} ) \\ \textbf{5} & \text{If } I_{bank, \ k} < I_{\epsilon}, \text{ remove } k \text{ from } S_{on} \\ & \text{Update } V_{array, \ k}^{CC}, \forall k \in S_{on} \text{ using } (1) \\ \textbf{7} & \textbf{until } both \ S_{on} \ and \ V_{array, \ k}^{CC}, \forall k \in S_{on} \ converge \\ \textbf{8} & \text{Update upper bound } V_{CTI}^{max} \text{ or lower bound } V_{CTI}^{min} \\ \textbf{9} & \forall k \in S: \ I_{bank, \ k}^{opt} \leftarrow I_{bank, \ k} \text{ if } k \in S_{on}; \ I_{bank, \ k}^{opt} \leftarrow 0 \\ & \text{otherwise} \\ \textbf{10} & \textbf{until } V_{CTI}^{max} - V_{CTI}^{min} \leq V_{\epsilon} \\ \textbf{11} & \textbf{return } \{I_{bank, \ k}^{opt}, \forall k \in S\}, \ S_{on}^{opt} \leftarrow S_{on}, \ V_{CTI}^{opt} \leftarrow V_{CTI} \\ \end{array}

```

# B. Global Charge Replacement

We consider the GCR optimization problem for discharge processes for a few hours using a military radio receiver as the load device [13]. We solve the GCR in a discrete time space. We discharge EES banks at a constant rate within each time slot. A simple method may solve a series of ICR problems one at each decision epoch to tackle the GCR problem, which may fail to achieve the global optimality due to its greedy nature. In fact, the near-optimal ICR solution prefers to discharge mainly from the supercapacitor arrays because of the higher cycle efficiency. It is highly likely that all the supercapacitor arrays may be fully discharged at very early stage. This in turn results in that the EES system should discharge the battery arrays at a significantly lower efficiency due to the rate capacity effect for the rest of the discharge process. Therefore, it is necessary to "globally consider the whole discharge process" and properly assign energy demands to different types of EES banks.

## **B.1** Estimation of Critical Power Level

We start from the fact that battery arrays are less efficient in supplying load demands at a high power rate because of their relatively large internal resistances and the rate capacity effect. Thus, we can have a better GCR efficiency by discharging the battery arrays at a relatively lower power rate while using the supercapacitor arrays to deal with sudden ramp-ups of the load demands. Inspired by this idea, we classify all the EES banks into two main categories without loss of generality: supercapacitor banks (SBs) and battery banks (BBs) according to their distinct properties. Our algorithm is also capable of accommodating more categories of the EES banks. We define effective energy/power of an EES bank as the energy/power delivered to load devices from the bank. We propose to seek for a *critical* power level, denoted by  $P^*(t), t \in [0,T]$ , defined as the maximum total amount of effective power that battery banks are responsible to provide at time t, i.e.,

$$E_{eff}^{SB} = \int_{0}^{T} P_{eff}^{SB}(t) = \int_{0}^{T} \max\{0, P_{load}^{total}(t) - P^{*}(t)\}dt, \qquad (13)$$

$$E_{eff}^{BB} = \int_{0}^{T} P_{eff}^{BB}(t) dt = \int_{0}^{T} \min\{P_{load}^{total}(t), P^{*}(t)\} dt, \tag{14}$$

where  $E_{eff}^{SB}$ ,  $P_{eff}^{SB}(t)$ ,  $E_{eff}^{BB}$ , and  $P_{eff}^{BB}(t)$  are the effective energy and power (at time t) provided by the SBs and BBs, respectively.  $P_{load}^{total}(t)$  is the total load power demands at time t. The critical power level  $P^*(t)$  is introduced to prevent fully discharging all the SBs at very early stage.  $E_{eff}^{SB}$  can be effectively estimated since we want to (nearly) fully discharge all the SBs at the end of discharge process. We may typically set  $E_{eff}^{SB}$  to be  $80\%\sim90\%$  of total energy initially stored in all the SBs to leave some margin for power loss due to power converters, internal resistances and self-discharge.

We propose to solve the GCR problem hierarchically. At top level, we globally consider the whole discharge process before discharge begins and find the time-dependent critical power level  $P^*(t)$ . To estimate the optimal  $P^*(t)$  efficiently, we assume that the efficiencies of power converters are all one, and the power loss due to internal resistances are negligible. At bottom level, we break the whole discharge process into many time slots. Then the bottom level problem becomes a series of ICR problems with additional constraints introduced by  $P^*(t)$ , to be solved by applying Algorithm 1 one at each decision epoch. The power losses are considered in the ICR problems at the bottom level.

At first, let us acquire some clues in determining optimal  $P^*(t)$  by neglecting self-discharge in supercapacitor arrays. In this case, all energy drawn from SBs is received by load devices. We formulate an optimization problem as follows:

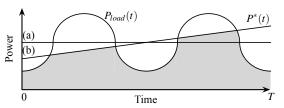

Fig. 4. Line (a) and (b) show the critical power level. The shadow area and white area under  $P_{load}(t)$  curve denote the effective energy provided by BBs and SBs, respectively.

**Given**: initial battery arrays SoCs,  $P_{load}^{total}(t), t \in [0, T], E_{eff}^{SB}$ .

**Find**: optimal  $P^*(t)$ ,  $t \in [0, T]$ .

Minimize: total energy drawn from battery arrays, i.e.,

$$E_{drawn}^{BB} = \int_{0}^{T} \sum_{k \in RR} V_{array,k}^{OC}(t) \cdot I_{array,k}^{\gamma_k}(t) dt.$$

(15)

**Subject to:**

$$\int_{0}^{T} \sum_{k \in BB} V_{array,k}^{OC}(t) \cdot I_{array,k}(t) dt = \int_{0}^{T} P_{load}^{total}(t) dt - E_{eff}^{SB}$$

(16)

$$\sum_{k \in RR} V_{array,k}^{OC}(t) \cdot I_{array,k}(t) = \min\{P_{load}^{total}(t), P^*(t)\}.$$

(17)

When neglecting OCV changes for battery arrays, it can be proved that the optimal solution is constant  $P^*(t)$  for  $t \in [0,T]$ , which is shown as Line (a) in Figure 4. The constant critical power level  $P^*(t) = P^*$  can be calculated using (13).

Now, we take into account the self-discharge of the supercapacitor arrays. According to (2), the self-discharge rate is proportional to the remaining energy in a supercapacitor array. Therefore, a straight line  $P^*(t) = \rho \cdot t + P^*(0)$  with positive slope  $\rho$  shown as Line (b) in Figure 4 can reduce the total self-discharge energy loss by discharging SBs faster at the early stage. Given slope  $\rho$ ,  $P^*(0)$  can be calculated by (13). We use  $E_{sd}^{SB}(\rho)$  to denote total energy loss in SBs due to self-discharge.

On the other hand, when slope  $\rho$  increases, more energy is consumed in battery arrays due to the rate capacity effect since for each battery array k,  $P_{drawn, k}(t)$  is a super-linear function of  $I_{array, k}(t)$  according to (3). We use  $E_{drawn}^{BB}(\rho)$  to denote the total energy drawn from battery arrays as a function of  $\rho$ . Therefore, the total energy drawn from HEES system  $E_{drawn}^{total}$  is a function of slope  $\rho$ , given by:

$$E_{drawn}^{total}(\mathbf{p}) = E_{eff}^{SB} + E_{sd}^{SB}(\mathbf{p}) + E_{drawn}^{BB}(\mathbf{p}). \tag{18}$$

Assuming  $E^{total}_{drawn}(\rho)$  is a quasi-convex function with respect to  $\rho$ , we can efficiently search in a proper range of  $\rho$  to find  $\rho_{opt}$  which minimizes  $E^{total}_{drawn}(\rho)$ , and then determine  $P^*(t)$ . The quasi-convex assumption is validated by experimental results.

# **B.2** Near-optimal Solution of GCR Problem

The GCR optimization problem can be solved in discrete time manner. At each decision epoch, we solve an ICR optimization problem using Algorithm 1 with an extra constraint given by:

$$V_{CTI}(t) \sum_{k \in RR} I_{bank,k}(t) \ge P_{eff}^{BB}(t) = \min\{P_{load}^{total}(t), P^*(t)\}.$$

(19)

Since this is an affine inequality constraint, the SICR problem can still be solved optimally in polynomial time. Therefore, we can obtain the near-optimal solution of GCR by solving a series of ICR problems with additional constraint one at each decision epoch. To improve the GCR solutions, we may refine the estimation of critical power level  $P^*(t)$  according to the actual remaining energy in supercapacitor arrays during the discharge process.

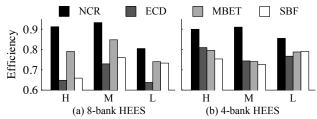

Fig. 5. Comparison of ICR efficiencies on eight-bank (a) and four-bank (b) HEES systems with high, median and low power demand.

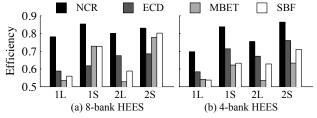

Fig. 6. Comparison of GCR efficiencies on eight-bank (a) and four-bank (b) HEES systems with load Profile 1 and 2, at long and short operation time.

#### V. EXPERIMENTS

We compare our near-optimal charge replacement control policy (NCR) derived from the previous section, with three baseline setups: equal current discharging (ECD, i.e., all banks are discharged at the same current), the most efficient bank tracking (MEBT, i.e., keep allocating power demand to the currently most efficient and not fully utilized bank until the load demand is satisfied), and the supercapacitor banks first (SBF, i.e., start with discharging all supercapacitor banks with the same current and discharge battery banks after the supercapacitor banks are fully discharged.)

#### A. Instantaneous Charge Replacement

We compare our near-optimal charge replacement policy with the baseline setups applying the above representative instantaneous discharge processes with a high (100 W), a medium (50 W) and a low (10 W) power demand to two different HEES systems. One consists of eight EES banks with four supercapacitor banks and four battery banks. We set the OCVs of the eight EES banks to 16 V, 16 V, 4 V, 4 V, 6 V, 6 V, 12 V, 12 V, respectively. The other HEES system consists of four EES banks with two supercapacitor banks and two battery banks. We set the OCVs of the four EES banks to 16 V, 4 V, 6 V, 12 V, respectively. Figure 5 shows up to 30% improvement in terms of charge replacement efficiency with our policy. We notice that the efficiencies of the baseline setups are strongly dependent on the environmental factor (e.g., load power) and the HEES system configuration (e.g., number of banks.) Thus no baseline setup consistently outperforms other baseline setups. Lacking of knowledge of the optimal CTI voltage, the efficiencies of baseline setups are not stable but typically fluctuate in a range of 5% along with the load power demand.

#### B. Global Charge Replacement

We use military radio receivers [13] as the load device, whose load profiles consist of periodic power demand levels of 10 W, 100 W, and 5 W for Profile 1, and 5 W, and 70 W for Profile 2 with a period of 10 minutes. We test our policy on Profile 1 and 2 with two different operating time cases: a long case for 8 hours and a short case for 4 hours. We assume all EES arrays are fully charged before discharge begins. Figure 6 shows that our near-optimal charge replacement policy consistently outperforms all baseline setups. The GCR efficiency improvements range up to 28% in eight banks HEES system (a) and 24% in four banks HEES system (b).

Comparing our policy with the baseline setups, we find that the aggressive baseline systems, such as MEBT and SBF, may perform well if the energy stored in the supercapacitor banks is capable of supporting the load demands in short operation time cases (Figure 6 (a) 2S.) However, our policy still outperforms these aggressive baseline setups due to better discharge control among different supercapacitor banks. Furthermore, significant GCR efficiency improvements against MEBT and SBF are observed in the long operation time cases because supercapacitor banks do not have enough energy while our policy exhibits near-optimal utilization of the energy from both the battery and supercapacitor banks. The conservative policy such as ECD leads to steady performance in all cases, but our policy still outperforms it by the near-optimal setting of the bank discharging currents, selective turning off the low efficiency banks to avoid constant controller power loss in the chargers and full utilization of energy in the high efficiency EES banks.

## VI. CONCLUSION

This paper introduced the global charge replacement (GCR) problem for hybrid electrical energy storage (HEES) systems, formulated it as a mixed-integer non-linear programming problem, and presented an efficient algorithm for finding a nearoptimal solution. We first obtained a critical power bound through global consideration of the HEES system properties and the load characteristics during the whole discharge process, and by estimating the energy contributions of each type of EES element arrays. We then solved the GCR problem in a discrete time manner. In particular, at each decision epoch, we solved an instantaneous charge replacement (ICR) problem with the aforesaid critical power bound. We generated a near-optimal solution of the ICR problem by applying effective heuristics to simplify it to a convex optimization problem. Experimental results demonstrate significant GCR efficiency improvement up to 30% against some baseline setups.

## REFERENCES

- [1] J. Baker and A. Collinson, "Electrical energy storage at the turn of the millennium," *Power Engineering Journal*, 1999.

- [2] T. Moore and J. Douglas, "Energy storage, big opportunities on a smaller scale," *EPRI J.*, 2006.

- [3] M. Pedram, N. Chang, Y. Kim, and Y. Wang, "Hybrid electrical energy storage systems," in *ISLPED*, 2010.

- [4] F. Koushanfar, "Hierarchical hybrid power supply networks," in *DAC*, 2010.

- [5] T. B. Atwater, P. J. Cygan, and F. C. Leung, "Man portable power needs of the 21st century: I. applications for the dismounted soldier. ii. enhanced capabilities through the use of hybrid power sources,," J. of Power Sources, 2000.

- [6] G. Sikha and B. N. Popov, "Performance optimization of a battery-capacitor hybrid system," *J. of Power Sources*, 2004.

- [7] H. Zhou, T. Bhattacharya, and A. M. Khambadkone, "Composite energy storage system using dynamic energy managementin microgrid applications," in *IPEC*, 2010.

- [8] D. Shin, Y. Wang, Y. Kim, J. Seo, M. Pedram, and N. Chang, "Battery-supercapacitor hybrid system for high-rate pulsed load applications," in *DATE*, 2011.

- [9] M. Chen and G. Rincon-Mora, "Accurate electrical battery model capable of predicting runtime and I-V performance," TEC, 2006.

- [10] D. Linden and T. B. Reddy, *Handbook of Batteries*. McGrew-Hill Professional, 2001.

- [11] Y. Choi, N. Chang, and T. Kim, "DC–DC converter-aware power management for low-power embedded systems," TCAD, 2007.

- [12] S. Boyd and L. Vandenberghe, Convex Optimization. Cambridge University Press, 2004.

- [13] Defense Advanced Research Projects Agency. http://www.sainc.com/LOTSTeaming/.